2026-01-27 18:56:58

SATA接口作为存储设备的核心连接通道,其ESD防护设计直接影响数据传输可靠性。本文从ESD管的工作特性、SATA总线信号规格、以及可能影响速度的特殊情况三个维度,系统分析ESD器件对SATA接口性能的影响机制,并基于实测数据与信号完整性原理,推荐适用于SATA 3.0/6Gbps场景的低电容ESD防护方案。

ESD保护器件(TVS/ESD二极管)在正常工作状态下呈现高阻抗特性,仅在检测到静电放电瞬态过压时导通泄放电流。其工作特性由三个核心参数决定:结电容(Cj)、钳位电压(Vc)与动态电阻(Rdyn)。

结电容对高速信号的影响机制: ESD器件的PN结电容与信号线并联,构成RC低通滤波器。当结电容超过一定阈值时,会导致高频信号分量衰减、上升沿变缓、眼图闭合度下降。对于SATA这类串行差分信号,结电容还会破坏差分对的阻抗平衡,引入共模噪声。

钳位电压与响应时间: 钳位电压必须低于后端SATA控制器芯片的耐压值(通常为3.3V或5V逻辑电平)。响应时间需小于1ns,确保在ESD脉冲上升沿(0.7-1ns)到达前完成钳位。阿赛姆ESD5C030TA的响应时间为ps级,满足亚纳秒级防护要求。

动态电阻与残压控制: 动态电阻(Rdyn)决定ESD电流泄放时的残压水平。Rdyn越低,相同电流下的钳位电压越低。阿赛姆ESDxx系列通过优化半导体材料和结构,可实现低至0.2Ω的动态电阻,在16A峰值电流下Vc可控制在8.5V以内。

漏电流与功耗: 正常工作状态下,ESD器件漏电流通常小于100nA,对SATA接口的功耗影响可忽略不计。阿赛姆车规级器件在125℃高温下漏电流仍低于1μA,满足7×24小时存储设备的长期稳定性要求。

SATA(Serial Advanced Technology Attachment)采用串行差分传输架构,各版本信号规格存在显著差异,对ESD器件的电容要求也随之变化。

SATA 1.0/1.5Gbps: 第一代SATA传输速率为1.5Gbps,信号上升时间约100ps。此速率下,ESD器件结电容可容忍至2-3pF,对信号完整性影响有限。使用普通TVS阵列(如结电容5pF)通常不会导致明显的眼图劣化。

SATA 2.0/3.0Gbps: 速率提升至3Gbps,信号基频提高至1.5GHz。根据信号完整性约束,ESD器件结电容需控制在1pF以下。此时若使用结电容超过2pF的器件,插入损耗在3GHz频点可能超过-1dB,导致眼图裕量下降15%以上。

SATA 3.0/6Gbps: 当前主流规格,传输速率达6Gbps,信号基频3GHz,上升时间缩短至约67ps。SATA规范要求差分对阻抗为100Ω±10%,任何并联电容都会降低差分阻抗,引起信号反射。此场景下,ESD器件结电容必须控制在0.5pF以下,理想值应低于0.3pF。

差分信号完整性要求: SATA采用两对差分线(TX±发送、RX±接收),差分对内的走线长度偏差需小于5mil(约0.127mm)。ESD器件若采用非对称布局或通道间电容差异过大(>0.05pF),将引入共模噪声,增加误码率。阿赛姆ESD5D100TA四通道阵列的通道间电容公差控制在±0.02pF以内,确保差分对完全对称。

阻抗匹配敏感性: SATA接口的阻抗匹配要求严格,差分阻抗需维持在100Ω±10%。ESD器件的寄生电容会等效降低线路阻抗,根据传输线理论,每增加0.1pF电容,在6Gbps速率下约引入0.5Ω的阻抗偏差。若ESD器件布局距离连接器超过5mm,走线电感(约0.5nH/mm)与器件电容形成的LC谐振可能进一步恶化信号质量。

在以下特定条件下,ESD防护器件确实可能对SATA硬盘读写速度产生可测量的影响。

结电容超标导致的信号衰减: 当ESD器件结电容超过SATA 3.0的容忍阈值(0.5pF)时,高频分量衰减显著。实测数据显示,使用结电容1.2pF的TVS器件在6Gbps速率下,插入损耗可达-1.5dB@3GHz,眼图张开度从标准的0.6UI降至0.45UI,误码率从10⁻¹²上升至10⁻⁹。这种信号完整性劣化会触发SATA控制器的自适应均衡机制,降低有效传输速率以维持链路稳定性。

差分对电容不平衡: 若ESD器件在多通道间的结电容存在偏差(如TX+通道0.3pF、TX-通道0.4pF),将破坏差分信号的对称性,产生共模噪声。共模噪声不仅降低信噪比,还可能通过地弹噪声影响电源完整性,导致硬盘控制器误判为信号质量下降,主动降速运行。阿赛姆ESD5D100TA阵列通过集成化设计确保四通道电容匹配度优于±0.02pF,避免此类问题。

布局不当引入的寄生参数: ESD器件距离SATA连接器超过10mm时,PCB走线引入的寄生电感(约0.5-1nH/mm)会与器件电容形成串联谐振。在6Gbps信号的3GHz基频附近,该谐振可能产生阻抗尖峰,导致信号反射系数增大。规范要求ESD器件应紧靠连接器布局(距离≤5mm),地线宽度≥3mm且至少配置2个地过孔,以最小化寄生电感。

多器件并联的电容叠加: 部分设计为增强防护能力而并联多个ESD器件,导致结电容叠加。例如两个0.6pF器件并联后总电容达1.2pF,超出SATA 3.0的容忍范围。此类设计在低速SATA 1.0/2.0场景可能正常工作,但在6Gbps速率下必然导致眼图闭合。阿赛姆建议单通道仅使用一颗低电容ESD器件(如ESD5C030TA,0.3pF),通过优化器件结构而非并联数量来提升IPP能力。

温度漂移导致的参数变化: 车规级或工业级SATA设备需在-40℃至85℃(或125℃)范围内工作。普通ESD器件的结电容随温度变化可达±20%,高温下电容增加可能导致夏季高温环境出现间歇性降速。阿赛姆车规级ESD器件通过AEC-Q101认证,在125℃环境下结电容漂移率控制在11.8%以内(从0.17pF增至0.19pF),确保全温度范围信号完整性稳定。

电源噪声耦合: ESD器件在泄放瞬态电流时,若接地路径阻抗过高(如地平面开槽或过长地线),会产生地弹噪声(Ground Bounce)。该噪声通过电源耦合可能影响SATA控制器的时钟恢复电路,导致相位抖动增加。SATA 3.0规范要求总抖动(TJ)小于0.15UI,地弹噪声可能占用其中30-40%的裕量。阿赛姆建议ESD器件地线直接连接至完整地平面,避免经过连接器地针回流。

深圳市阿赛姆电子有限公司针对SATA接口的信号完整性与防护需求,提供全系列低电容ESD解决方案。

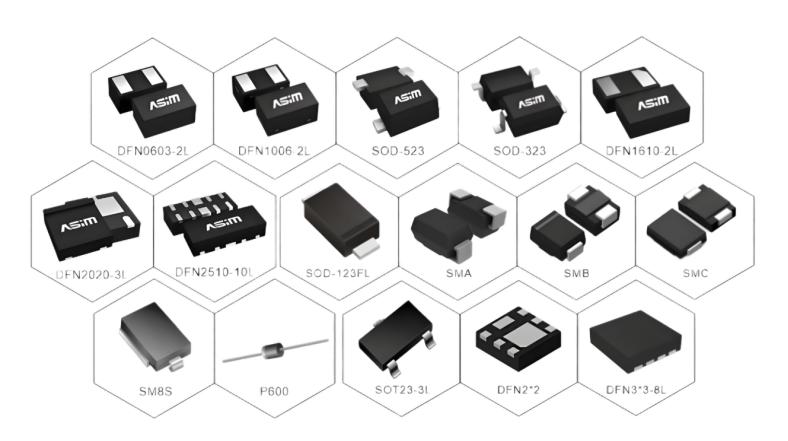

ESD5C030TA(推荐用于SATA 3.0): 结电容典型值0.3pF(@1MHz),满足SATA 6Gbps速率要求。工作电压5V,钳位电压8.5V@16A(TLP测试),符合IEC 61000-4-2 Level 4标准(±8kV接触放电/±15kV空气放电)。采用DFN0603-2L封装(0.6×0.3mm),寄生电感低于0.3nH,适合紧贴SATA连接器布局。

ESD3V3E0017LA(高速场景): 结电容0.17pF(典型值),支持高达48Gbps的传输速率,远超SATA 3.0的6Gbps需求。在SATA接口中使用时,插入损耗仅0.12dB@3GHz,眼图裕量损失小于8%。该器件通过AEC-Q101 Grade 0认证,适用于车规级存储设备。

ESD5D100TA(四通道阵列): 专为SATA/eSATA的多差分对设计,单芯片集成4通道保护,每通道结电容0.3pF,通道间电容匹配度±0.02pF。流通式封装(Flow-through)简化PCB布局,减少布线不连续性,确保TX±与RX±两对差分线的对称性。

技术验证支持: 阿赛姆深圳EMC实验室配备Keysight网络分析仪(频率范围1MHz-12GHz)、高速示波器(带宽≥12GHz)及SATA协议分析仪,可针对客户实际PCB进行眼图测试、S参数扫描与误码率验证。实验室支持SATA 3.2合规性测试,包括眼图高度/宽度、S21插入损耗、S11回波损耗等关键指标测量。

选型指导: 阿赛姆技术团队提供从威胁等级评估、SATA版本适配(1.5Gbps/3Gbps/6Gbps)、器件选型到PCB布局审查的全流程支持。针对SATA 3.0应用,推荐结电容<0.5pF的器件;针对企业级SSD的7×24小时高可靠性场景,推荐通过AEC-Q101认证的车规级器件。

SATA接口ESD管是否会拖慢硬盘读写速度,取决于器件结电容、布局位置与SATA版本的匹配度。在SATA 3.0/6Gbps场景下,若选用结电容低于0.5pF的低电容ESD器件(如阿赛姆ESD5C030TA或ESD3V3E0017LA),并遵循紧靠连接器(≤5mm)、差分对称布局、完整地平面回流等设计原则,ESD防护不会成为速度瓶颈。反之,若使用结电容超过1pF的普通TVS或布局不当,确实可能导致眼图闭合、误码率上升与速率降级。工程师选型时应重点关注器件的S参数模型与实测眼图数据,而非仅关注ESD防护等级。